先进的微处理器从碳纳米管内完成

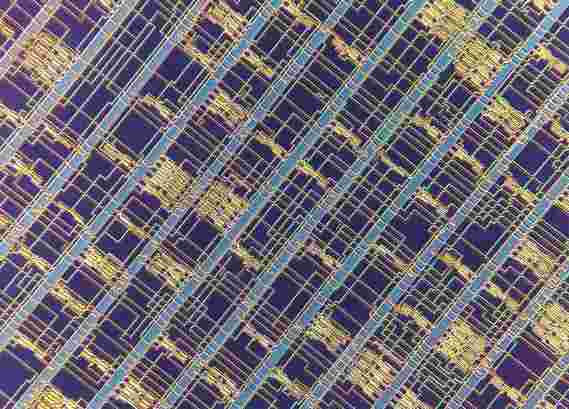

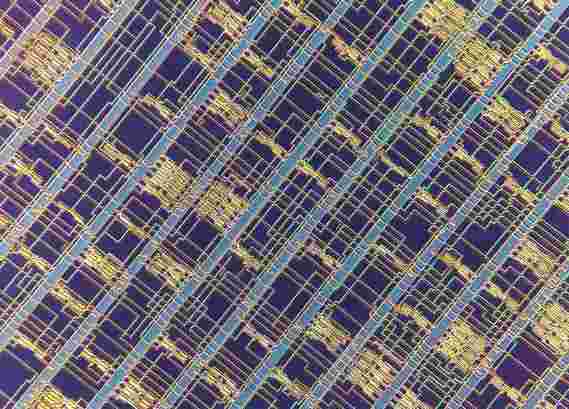

关闭由碳纳米管场效应晶体管构建的现代微处理器。

新方法利用相同的制造工艺用于硅芯片,为下一代计算机提供关键进步。

经过多年的解决多年的设计和制造挑战,麻省理工学院研究人员已经从碳纳米管晶体管建造了现代微处理器,这些微处理器被广泛被视为更快,更环保的硅对手。

今天描述的微处理器可以使用传统的芯片制造工艺建造,可以使用传统的芯片制造工艺建造,这是制造碳纳米管微处理器更实用的主要步骤。

硅晶体管 - 关键微处理器组件在1到0位开关计算 - 已携带计算机行业数十年。正如摩尔定律所预测的那样,行业已经能够在每隔几年内收缩到筹码上的碎片,以帮助执行越来越复杂的计算。但专家现在预见了硅晶体管将停止缩小的时间,并且变得越来越低。

制造碳纳米管场效应晶体管(CNFET)已成为建立下一代计算机的主要目标。研究表明,与硅相比,CNFET具有承诺的能量效率和更大速度远远超过10倍。但是,在按比例制造时,晶体管通常会带来许多影响性能的缺陷,因此它们保持不切实际。

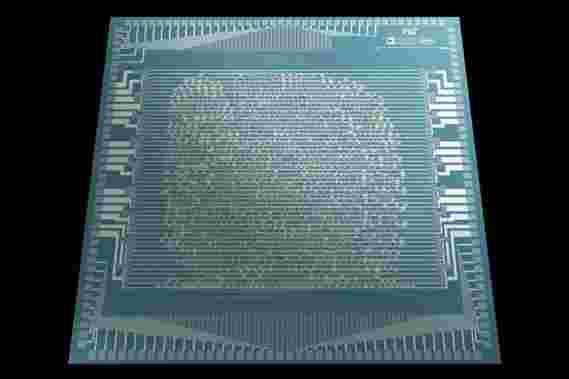

麻省理工学院研究人员发明了新技术,以利用传统的硅芯片铸造厂中的工艺在制造CNFET中进行极限缺陷并在制造CNFET中进行全功能控制。它们展示了一个16位微处理器,具有超过14,000个CNFET,可执行与商业微处理器相同的任务。自然纸张描述了微处理器设计,包括70多页,详细说明了制造方法。

微处理器基于RISC-V开源芯片架构,该架构具有微处理器可以执行的一组指令。研究人员的微处理器能够准确地执行全套指令。它还执行了经典“Hello,World!”的修改版本。计划,打印出来,“你好,世界!我是rv16xnano,由cnts制成。“

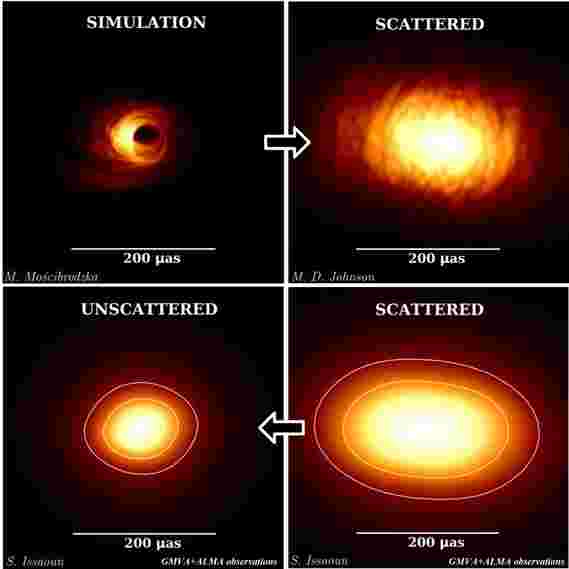

麻省理工学院工程师已经建立了一种从碳纳米管场效应晶体管(所示)的现代微处理器,它们看起来比硅晶体管更快和更环保。新方法使用用于硅芯片的相同的制造方法。

“这是迄今为止,由任何新兴纳米技术进行的最先进的芯片,这是高性能和节能计算的,”Emanuel E Landsman Career Developon Assistant of Electrical Engineer及计算机教授科学(EECS)和MicroSystems技术实验室的成员。“硅有限。如果我们希望在计算中继续获得增益,碳纳米管代表了最有希望的克服这些限制的方法之一。[本文]完全重新投入我们如何使用碳纳米管构建芯片。“

加入守卫本文是:第一作者和博士山,研究生刘,安德鲁赖特,迈克迪夫·威斯特(Andrew Wright),Tathagata Srimani,Pritpal Kanhaiya,Rebecca Ho和Aya Amer,所有EEC; Arvind,约翰逊计算机科学与工程教授,计算机科学与人工智能实验室研究员; Anantha Chandrakasan,工程学院的院长和Vannevar布什电气工程和计算机科学教授;和塞缪尔富勒,yosi stein和denis murphy,所有的模拟设备。

与CNFETS的“BANE”战斗

微处理器在六年前由南普拉特和其他研究人员设计的先前迭代,只有178个CNFET,并在一点数据上运行。从那时起,南议员和他的麻省理工学院同事在生产设备时解决了三种特定的挑战:材料缺陷,制造缺陷和功能问题。山丘做了大部分微处理器设计,而Lau则处理大部分制造。

多年来,固有的缺陷到碳纳米管是一个“野外的祸根”,Shulaker说。理想地,CNFET需要半导体性能,以将它们的电导率切换为OFF,对应于比特1和0。但不可避免地,一小部分碳纳米管将是金属的,并且会慢或阻止晶体管切换。为了对这些故障造成的稳健,高级电路需要碳纳米管,含量约为99.99999999%纯度,这几乎不可能产生今天。

研究人员提出了一种叫做梦想的技术(一种用于对金属CNTS的弹性术语的首字母缩写),其定位金属CNFET的方式,使得它们不会破坏计算。在这样做时,他们放宽了严格的纯度要求大约四个数量级 - 或者10,000次 - 例如,它们只需要碳纳米管约99.99%的纯度,目前可能。

设计电路基本上需要连接到晶体管的不同逻辑门库,这些晶体管可以组合于,例如,创建添加剂和乘法器 - 将字母中的字母组合以创建单词。研究人员意识到金属碳纳米管不同地影响了这些门的不同配对。例如,栅极A中的单个金属碳纳米管可以破坏A和B之间的连接。但是栅极B中的几种金属碳纳米管可能不会影响其任何连接。

在芯片设计中,有很多方法可以在电路上实现代码。研究人员运行模拟以查找将具有稳健的所有不同的栅极组合,并且对任何金属碳纳米管都不会稳健。然后,他们定制了一种芯片设计程序,以自动学习最不可受金属碳纳米管影响的组合。在设计新芯片时,该程序将仅利用强大的组合并忽略易受攻击的组合。

“梦想'双关语是非常有意义的,因为这是梦想解决方案,”南·福克斯说。“这使我们可以从架子上购买碳纳米管,将它们放在晶圆上,只需像正常一样建立我们的电路,而不会有其他特殊的事情。”

去角质和调整

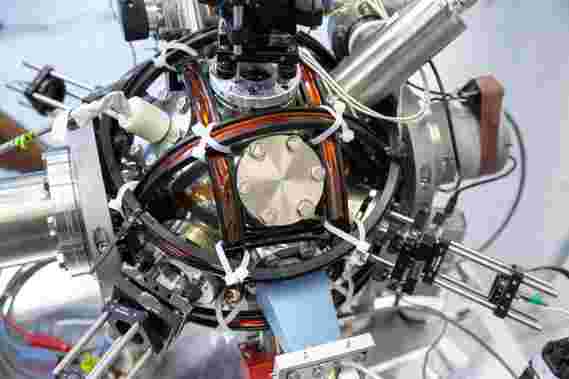

CNFET制造从溶液中的碳纳米管沉积在具有预测的晶体管架构的晶片上。然而,一些碳纳米管不可避免地将随机粘在一起以形成大束状 - 类似的意大利面条,形成为小球 - 形成芯片上的大颗粒污染。

为了清洁这种污染,研究人员通过选择性剥离来创造冲洗(用于“除去孵育的纳米管”)。用促进碳纳米管粘附的药剂预处理晶片。然后,将晶片涂有一定的聚合物并浸入特殊溶剂中。脱离聚合物,它只携带大束,而单个碳纳米管保持粘附在晶片上。与类似方法相比,该技术导致芯片上的粒子密度降低约250倍。

最后,研究人员用CNFETS解决了常见的功能问题。二进制计算需要两种类型的晶体管:“n”类型,用0位和0位和“p”类型的1位和关闭,与之相反。传统上,使两种类型的碳纳米管造成挑战,通常产生随着性能而变化的晶体管。对于此解决方案,研究人员开发了一种称为混合(用于静电掺杂的“金属界面工程”)的技术,其精确地调谐功能和优化晶体管。

在该技术中,它们将某些金属连接到每个晶体管-Platinum或钛 - 这允许它们将该晶体管固定为P或N.然后,它们通过原子层沉积涂覆氧化物化合物中的CNFET,这使得它们允许它们调整特定应用的晶体管特性。例如,服务器通常需要采用非常快速但使用能量和功率的晶体管。另一方面,可穿戴设备和医疗植入物可以使用较慢的低功率晶体管。

主要目标是将芯片放入现实世界中。为此,研究人员现在开始通过通过国防高级研究项目机构通过计划将其制造技术实施到硅芯片铸造中,支持该研究。虽然没有人可以说,当碳纳米管完全从碳纳米管击中架子时,南瓜说,它可能是少于五年。“我们认为它不再是一个问题,但是什么时候,”他说。

该作品也得到了模拟设备,国家科学基金会和空军研究实验室的支持。

-

富含钠的家用成分帮助生长碳纳米管

2022-02-23 -

麻省理工学院航空航天工程师开发碳纳米管“针脚”加强复合材料

2021-12-09 -

镓氮化镓电子设备大大降低了能源使用

2021-10-16 -

新的硫化钼晶体管显着优于现有型号

2021-10-03 -

基于石墨烯的超级电容器可以显着提高电动车辆的力量

2021-09-30 -

研究人员开发由石墨烯和碳纳米管制成的Spaser

2021-09-24 -

工程师构建碳纳米管电脑

2021-09-16 -

研究人员创造了世界上最快的有机晶体管

2021-09-11 -

对齐的碳纳米管 - 硅片可提高电池设计

2021-09-09 -

研究人员开发了没有半导体的晶体管

2021-09-07